Bimo Prasetyo Wibowo | 2D TI

NIM : 2103015177

Latches, Flip-Flop and Pewaktu (Timer)

Dengan cara yang sama bahwa gerbang adalah blok bangunan sirkuit kombinatorial, kait dan sandal jepit adalah blok bangunan sirkuit sekuensial. Sementara gerbang harus dibuat langsung dari transistor, kait dapat dibuat dari gerbang, dan sandal jepit dapat dibuat dari kait. Fakta ini akan membuatnya lebih mudah untuk memahami kait dan sandal jepit.

Baik kait maupun flip-flop adalah elemen rangkaian yang outputnya tidak hanya bergantung pada input saat ini, tetapi juga pada input dan output sebelumnya. Perbedaan antara latch dan flip-flop adalah bahwa latch tidak memiliki sinyal clock, sedangkan flip-flop selalu memiliki sinyal clock.

Latches

Bagaimana kita bisa membuat rangkaian dari gerbang yang tidak kombinatorial? Jawabannya adalah umpan balik, yang berarti bahwa kita membuat loop dalam diagram rangkaian sehingga nilai keluaran bergantung, secara tidak langsung, pada dirinya sendiri. Jika umpan balik tersebut positif maka rangkaian cenderung memiliki keadaan stabil, dan jika negatif rangkaian akan cenderung berosilasi.

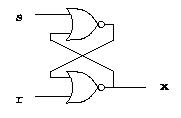

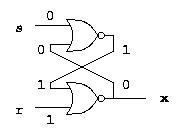

Kait memiliki umpan balik positif. Berikut adalah contoh kait sederhana:

Kait ini disebut SR-latch, yang merupakan singkatan dari set dan reset.

Tidak praktis untuk menggunakan metode yang telah kami gunakan untuk menggambarkan rangkaian kombinatorial untuk menggambarkan perilaku SR-latch. Kemudian, kami akan menunjukkan metode untuk menggambarkan flip-flop dan sirkuit sekuensial clock. Untuk saat ini, kami hanya mengandalkan intuisi kami untuk menggambarkan cara kerja kait.

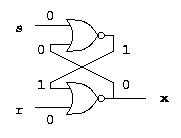

SR-latch dimaksudkan untuk memiliki paling banyak satu inputnya sama dengan 1 setiap saat. Ketika kedua inputnya adalah 0, ia memiliki dua status stabil yang berbeda. Entah x adalah 0, dalam hal ini kami memiliki nilai sinyal berikut:

atau x adalah 1, dalam hal ini kita memiliki nilai sinyal berikut:

Nilai sebenarnya tergantung pada riwayat nilai input seperti yang akan kami tunjukkan selanjutnya.

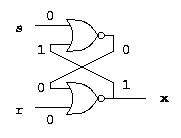

Sekarang anggaplah s adalah 1 (dan oleh karena itu r adalah 0 karena kami mengizinkan paling banyak satu input menjadi 1 setiap saat). Kami mendapatkan nilai sinyal berikut:

1 pada input s memastikan output gerbang nor atas adalah 0, dan dua 0 pada input gerbang nor bawah memastikan output x adalah 1.

Sekarang anggaplah input s berubah dari 1 ke 0, sedangkan input r tetap pada 0. Input kedua dari gerbang nor atas adalah 1, jadi transisi dari 1 ke 0 dari input s, tidak membuat perbedaan. Keluaran x tetap pada 1. Dalam hal ini, jika masukan s dan r keduanya 0, hanya ada satu kemungkinan keadaan stabil, keadaan yang memberikan nilai x 1.

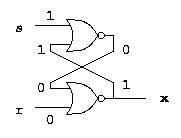

Sebaliknya, misalkan r adalah 1 (dan oleh karena itu s adalah 0 karena kami mengizinkan paling banyak satu input menjadi 1 setiap saat). Kami mendapatkan nilai sinyal berikut:

d

d Angka 1 pada input r memastikan output x adalah 0, dan dua 0 pada input gerbang nor atas memastikan output gerbang nor atas adalah 0.

Sekarang anggaplah input r berubah dari 1 ke 0, sedangkan input s tetap pada 0. Input kedua dari gerbang nor-bawah adalah 1, jadi transisi dari 1 ke 0 dari input r, tidak membuat perbedaan. Keluaran dari gerbang nor atas tetap pada 1. Dalam hal ini, jika input s dan r keduanya 0, hanya ada satu kemungkinan keadaan stabil, keadaan yang memberikan x nilai 0.

Dari pembahasan di atas, kami menyimpulkan bahwa SR-latch mampu mengingat keadaan terakhir dari input, dalam arti mengingat yang mana dari dua input, s atau r, yang terakhir bernilai 1.

Saat kita perlu menggambar SR-latch, kita menggunakan simbol berikut:

Flip-flops

Latch tidak sinkron, yang berarti bahwa output berubah segera setelah input berubah. Sebagian besar komputer saat ini, di sisi lain, adalah sinkron, yang berarti bahwa output dari semua rangkaian berurutan berubah secara bersamaan dengan ritme sinyal jam global.

Flip-flop adalah versi sinkron dari latch. Untuk lebih memperumit situasi, ada beberapa tipe dasar sandal jepit. Di sini, kita hanya akan mempertimbangkan jenis yang disebut flip-flop master-slave.

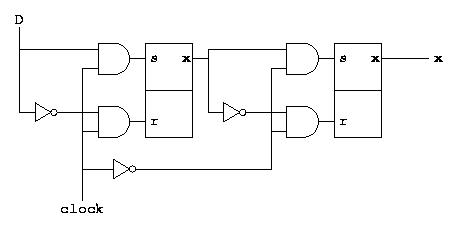

Selain tipe dasar flip-flop, ada variasi kecil tergantung pada jumlah input dan bagaimana mereka mengontrol keadaan flip-flop. Di sini, kita hanya akan mempertimbangkan jenis flip-flop yang sangat sederhana yang disebut D-flip-flop. D-flip-flop master-slave dibangun dari dua SR-latches dan beberapa gerbang. Berikut adalah diagram sirkuit:

SR-latch paling kiri disebut master dan paling kanan disebut slave.

Mari kita pertimbangkan terlebih dahulu apa yang terjadi ketika sinyal clock adalah 1. Dalam hal ini, dua gerbang-dan di depan input master terbuka, yaitu, mereka membiarkan nilai input-D melalui input s dari master, dan kebalikan dari input D ke input r dari master. Dengan demikian, nilai input D akan langsung melalui master ke output x dari master. Tetapi dua gerbang-dan dari slave ditutup kembali, yaitu outputnya selalu 0, jadi slave mempertahankan nilai lamanya.

Sebaliknya, ketika sinyal clock adalah 0, kebalikannya benar, yaitu, gerbang-dan pada input master tertutup, sedangkan yang pada input slave terbuka. Dalam hal ini, flip-flop sama sekali tidak sensitif terhadap perubahan input.

Sekarang, mari kita perhatikan apa yang terjadi ketika jam bergerak dari 1 ke 0. Agar ini berfungsi, kita harus mengasumsikan bahwa input tetap sama selama periode singkat dari kanan sebelum ke kanan setelah sinyal jam berubah. Hal pertama yang terjadi adalah gerbang-dan pada input master mati, yaitu, mereka menjadi tidak sensitif terhadap perubahan input lebih lanjut. Nilai keluaran x dari master sekarang menjadi nilai masukan D tepat sebelum jam mulai berubah. Beberapa saat kemudian, transisi sinyal clock telah melewati inverter dan mencapai gerbang-dan dari slave. Gerbang ini terbuka, memungkinkan output x dari master disebarkan ke nilai x dari slave. Nilai x dari slave, dan oleh karena itu nilai seluruh flip-flop sekarang berisi nilai input D tepat sebelum jam mulai berubah. Kita dapat mengatakan bahwa transisi jam menyalin input ke output flip-flop. Tetapi tidak pernah ada jalur langsung dari input ke output. Output berubah hanya sebagai akibat dari transisi jam dari 1 ke 0.

Akhirnya, mari kita lihat apa yang terjadi ketika jam bergerak dari 0 ke 1. Pertama, gerbang dan master terbuka, membiarkan nilai input D masuk ke master. Pada saat nilai D mencapai master, transisi sinyal clock mencapai gerbang-dan dari slave, dan mematikannya sebelum output yang mungkin dimodifikasi dari master mencapai slave. Jadi, budak itu mempertahankan nilai lamanya. Dari luar, sepertinya tidak ada yang terjadi, karena outputnya tidak berubah. Namun, mulai sekarang, master terbuka untuk perubahan input.

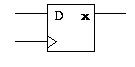

Berikut adalah simbol yang kami gunakan untuk D-flip-flop:

Segitiga kecil untuk input jam menunjukkan bahwa input ini sensitif hanya untuk transisi yang bertentangan dengan level seperti yang dijelaskan dalam paragraf sebelumnya. Terkadang kita tidak menggambar input jam sama sekali ketika dipahami bahwa itu ada di sana. Sinyal jam membosankan karena semuanya hanya terhubung satu sama lain. Oleh karena itu tidak ada gunanya menggambar semuanya, dan dengan demikian mengacaukan diagram yang tidak perlu.

Tidak ada komentar:

Posting Komentar